1. 概述

电源完整性: 如何保证电源分配系统(Power Distribution Network—— PDN)满足负载芯片对电源的要求,即为电源完整性。

解释一下,即电源调整系统为各部分电路提供稳定正确的工作电压,使系统的各部分能在负载电流发生变化时依然能够保持稳定。能够对系统因状态变化或者受到某些影响(比如:电压波动、串扰、反射、辐射、噪声等)进行有效抑制。

PDN 系统的作用:

(1)为负载提供干净的供电电压;

(2)为信号提供低噪声的参考路径(返回路径);

(3)减轻电磁干扰(EMI)问题。

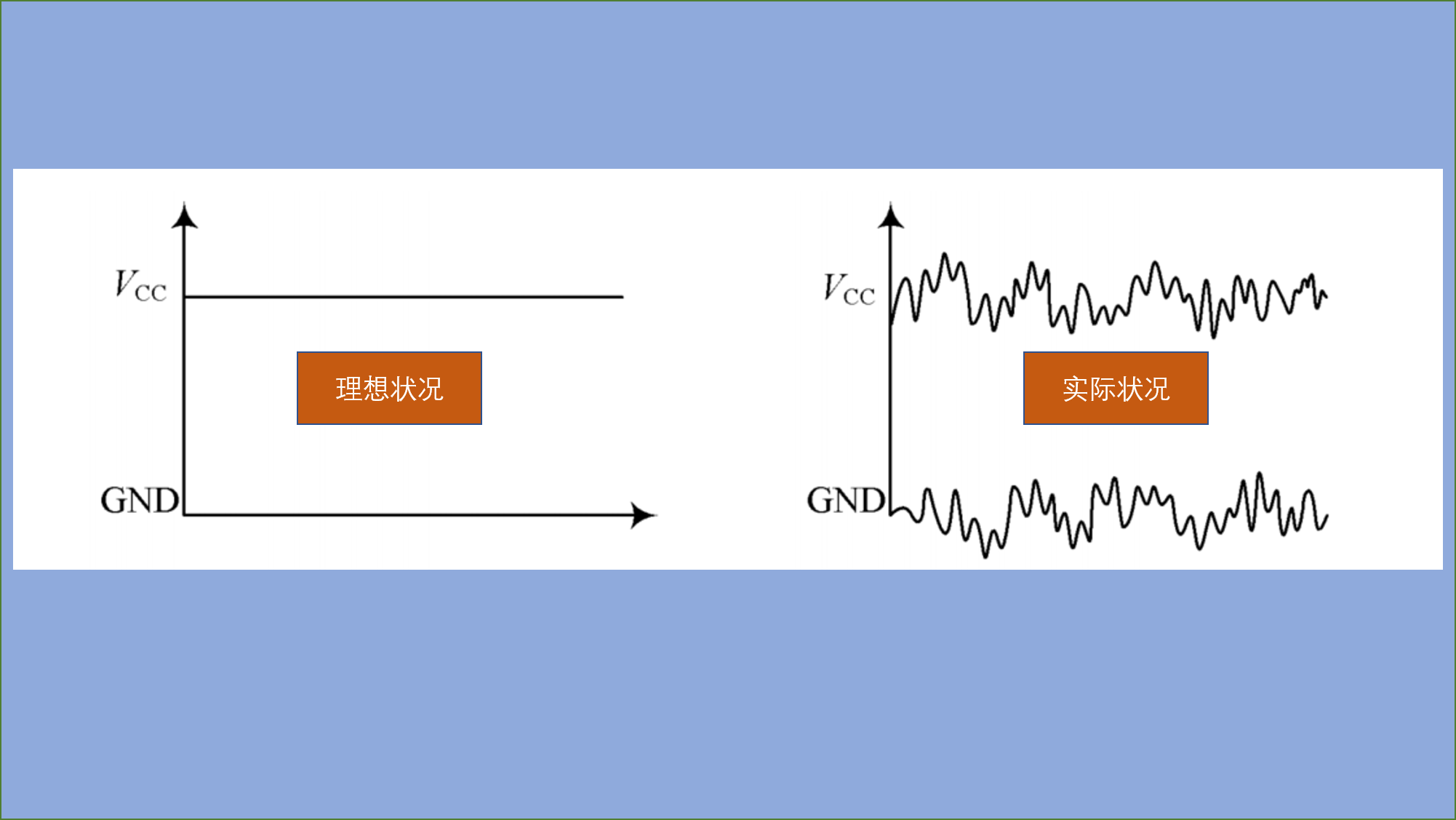

理想的电源系统的阻抗为 0 ,但是实际中是存在各种各样额噪声,电路是在一定程度的噪声容限下工作的,如果电源的噪声超出了系统允许的范围,就有可能导致系统不能按照既定的方式正常运行。

当芯片内部的晶体管的翻转的时候需要从 PDN 系统汲取电流,只要芯片端的电源分配网络的输入阻抗足够低,那么在这个过程中的压降也会降低,保持芯片电源的稳定(在噪声容限内波动不影响芯片的正常工作)

2. 造成电源完整性问题的原因

先分析一下影响电源完整性的原因,找到了病根,才好对症下药。

随着芯片的开关速度越来越快(上升时间越来越小),芯片内的开关管不可能同步完成转换,当一部分的晶体管已经完成稳定转换,而另一部分则还在转换之中,状态的不同步就造成电源早上在芯片内部传递,可能导致某些不定态的晶体管输出状态错误。

芯片的开关速度不断提高,导致瞬态电流和功耗都随之增加。

电源分配系统的噪声来源:

|编号|原因|

|:—:|:—-:|

|1|电源稳压芯片自身的输出存在噪声,DC-DC 的输出纹波就比 LDO 大|

|2|电源的输出无法对负载电流的快速变化实时响应,造成电压跌落|

|3|电源路径和地回路都存在一定的阻抗,电流经供电回路不可避免的存在压降,瞬态电流的变化就造成负载电压的波动|

|4|高速信号通过过孔换层引起电源噪声|

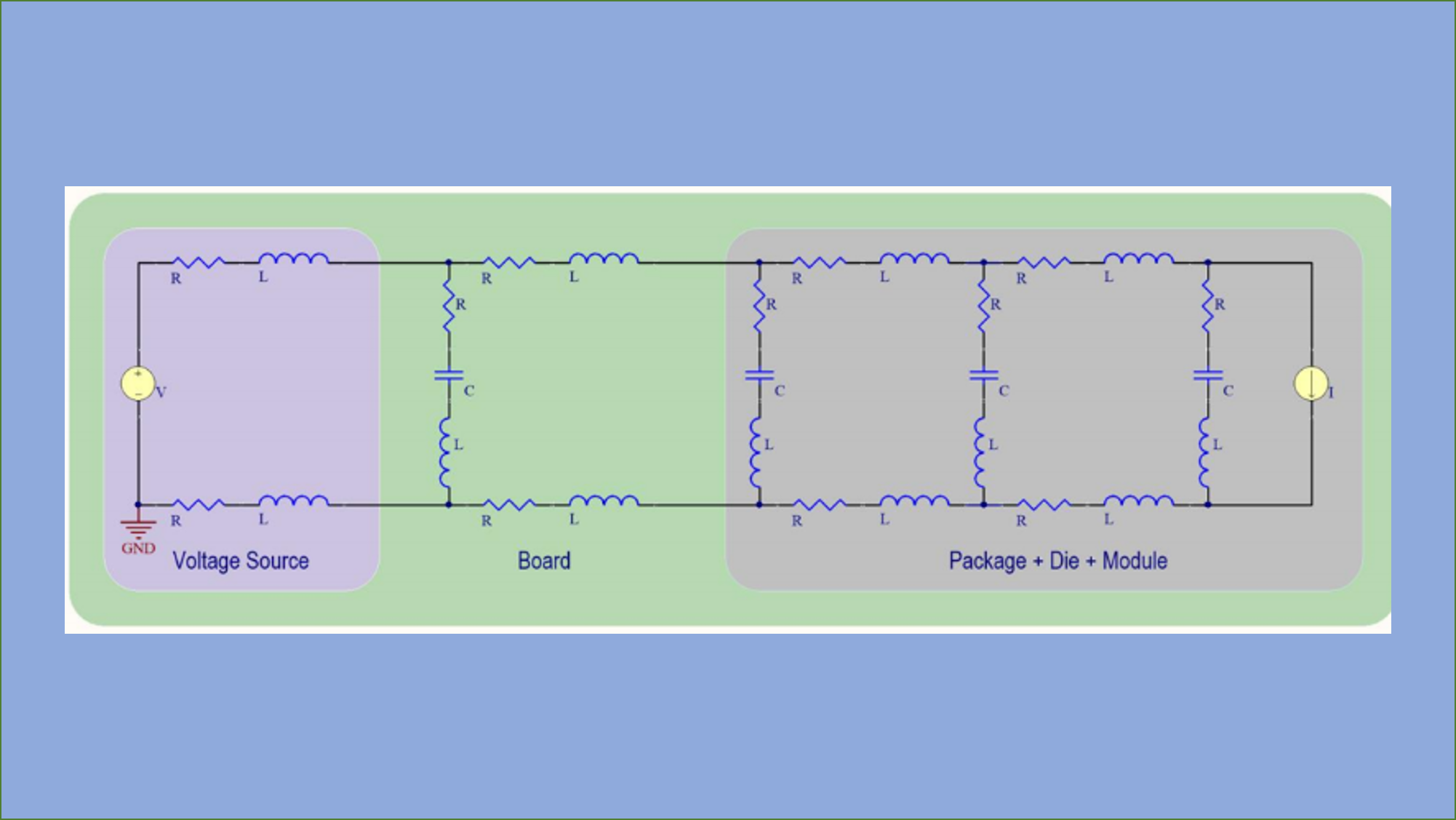

3. PDN 系统

电源分配网络包括:电压调整模块(Voltage Regulator Module)到电路板上各部分电源之间的互相连接,具体为电路板上的电源平面、地平面、连线、电缆、接口

、电容等。

PDN 系统模型如下图所示,从左往右依次是 PCB 的 PDN,芯片封装的 PDN。

4. PDN 之 RLC

4.1 电阻(R)

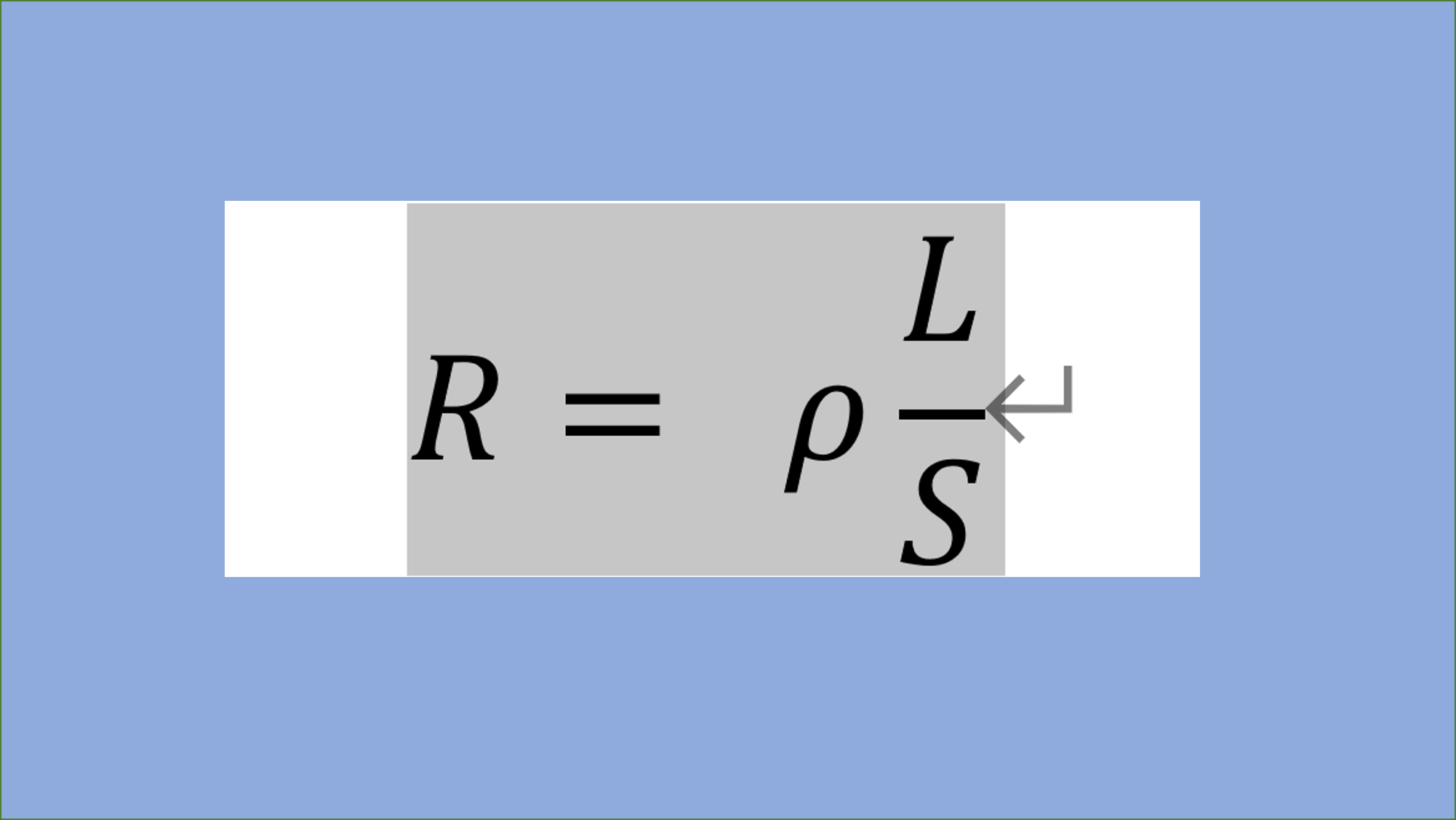

电阻是表征导体对直流电流的阻碍作用。当回路中,一段导体有电流流过时,电阻的作用表现为电能转化为热能(I^2 R),在导体的两端产生一定的压降(U = IR)。电阻的大小与导体的材料,长度,横截面积,温度有关。

电源分配系统上的电阻产生的损耗会导致电能转换为热能被丧失掉,同时温度的升高又对电路或一些器件造成影响,从而影响系统的稳定性和可靠性。如果某些部分电流持续增大甚至会导致该部分的电路烧毁。

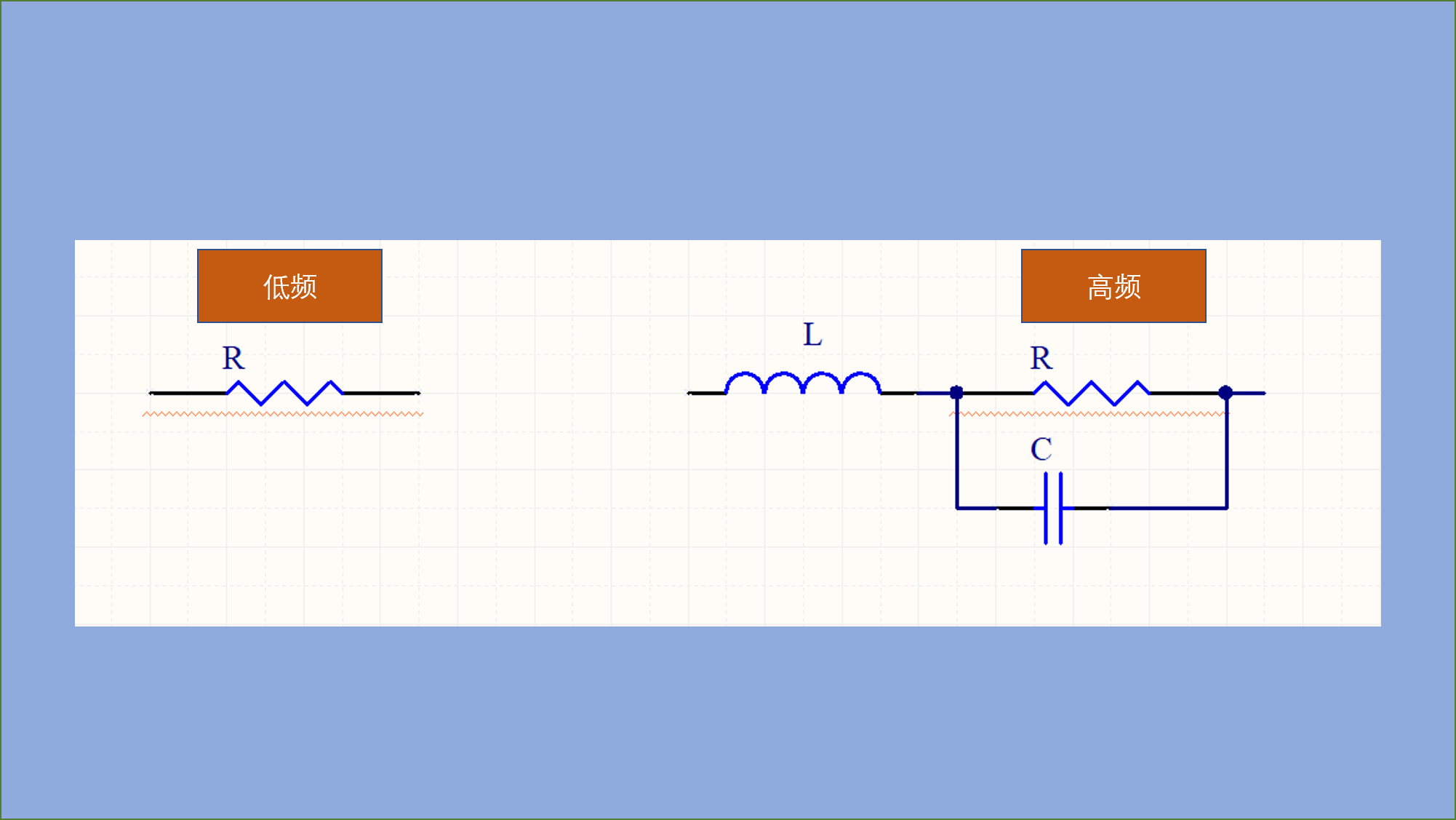

下图为电阻在低频和高频下表现出来的特性:

4.2 电感(L)

电感是表征导体对交变电流阻碍作用的物理量。当导体中有电流流过时,会在导体的周围形成磁场。当电流变化时,周围的磁场也会发生变化,在导体的两端形成感应电动势,形成的感应电动势形成的电流反过来阻碍原有电流的变化。即电感是:通直流,阻交流。这样形成的电感称之为自感(L)。当两个支路距离比较近,两个支路之间的互相影响称之为互感(M)。

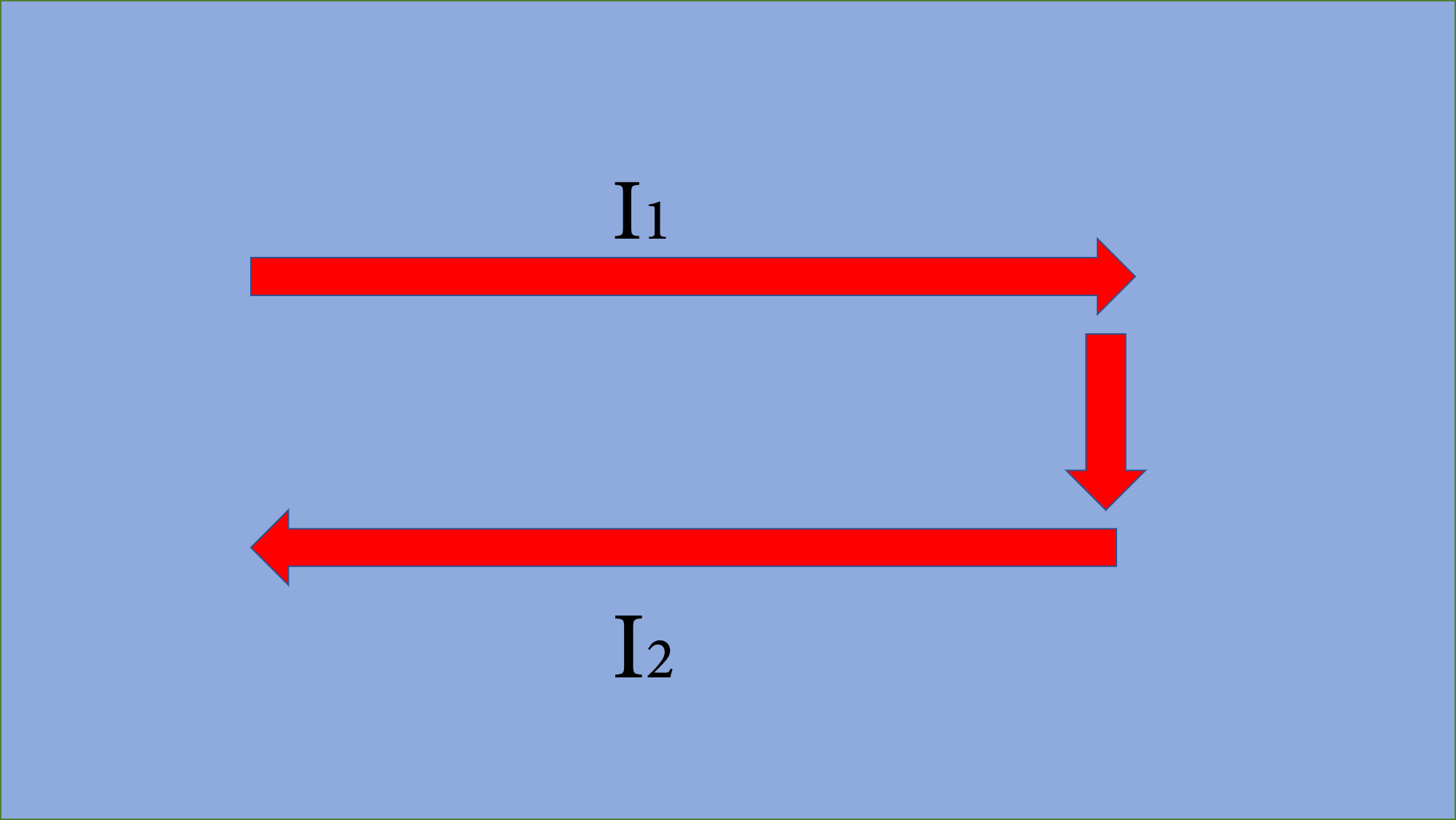

如上图所示的一个完整回路,Ia 表示正向的电源回路,Ib 表示方向的地回路。两个回路各自存在自感,而互相之间又存在互感。当回路上的电流发生变化时,在电感的周围就形成磁场,电流变化增大,电感增强,而互感是阻碍自感的变化的。

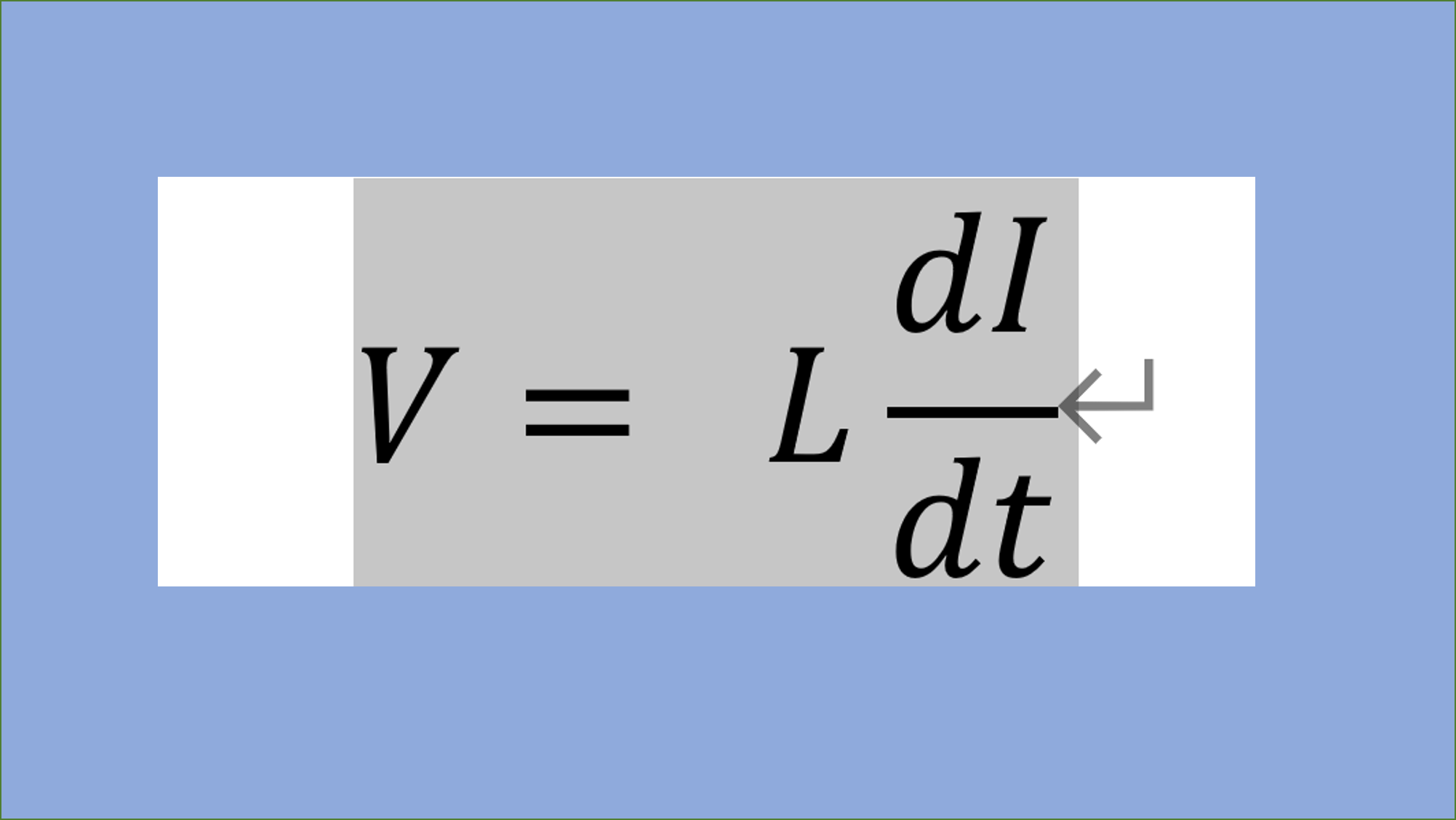

如上图的公式,电流的变化必然造成电路上电压的变化,对于正向,造成的问题就是稳压器的输出与芯片的输入端电压不一致,V 就是电源路径上的噪声,造成电源轨道塌陷。而在返回的回路上(一般是地),因为存在一个 V 大小的电压,导致地平面发生变化,造成地弹噪声。

可知: 由于电流变化引起的感应电动势的变化是产生电源噪声的原因,如何减弱这种影响,也就是有效的对系统的电源完整性进行控制。

措施:

(1)尽量减小回路中电流的变化率,稳定负载的变化造成电流的瞬变,稳定电流的大小;

(2)减少电路走线、接线的电感,这就是走线尽可能短、宽的原因,减少电路本身的自感。

4.3 电容(C)

去耦电容是目前电路中解决电源噪声的主要方式,此处也主要是对针对电容的去耦作用。

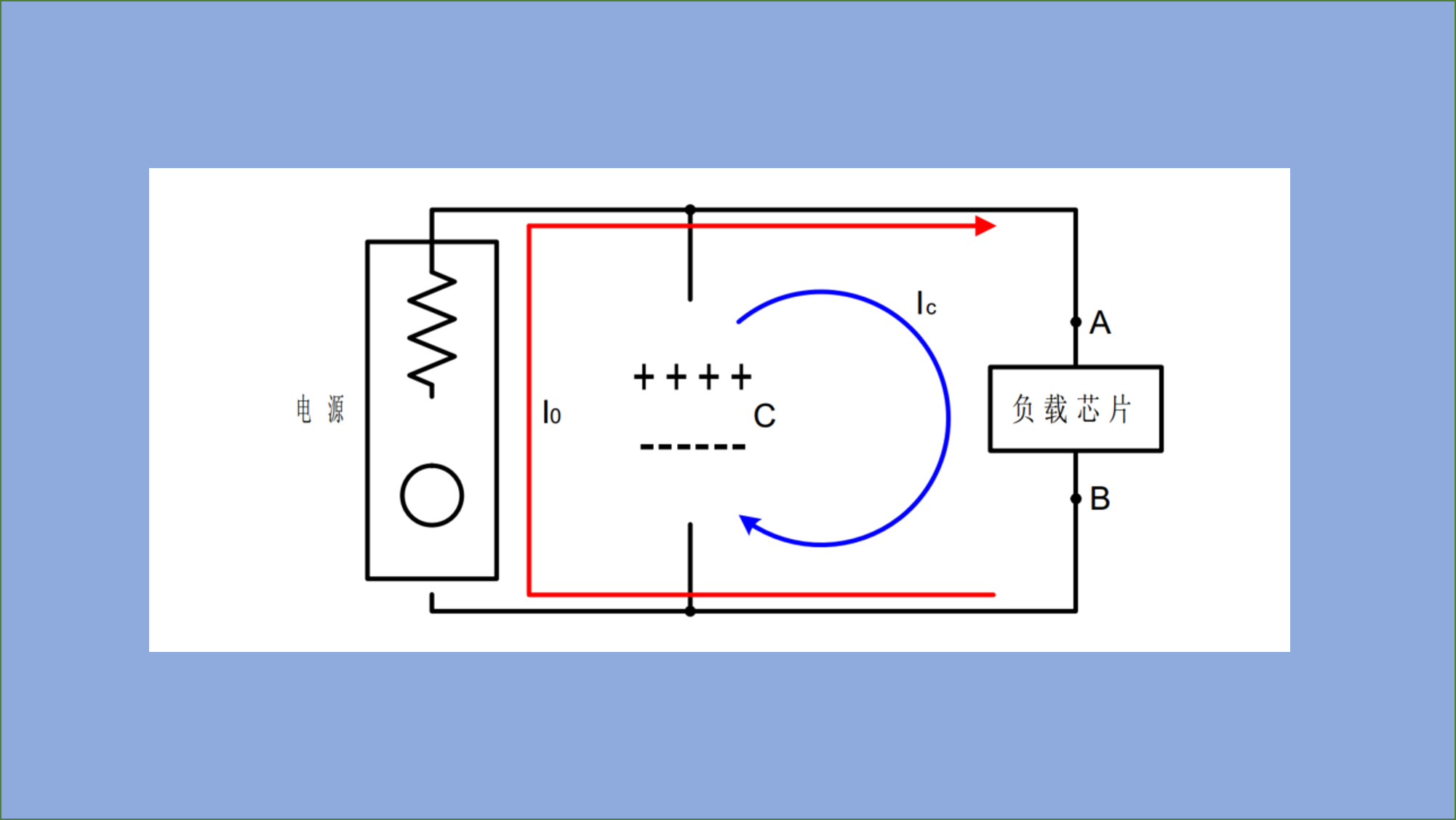

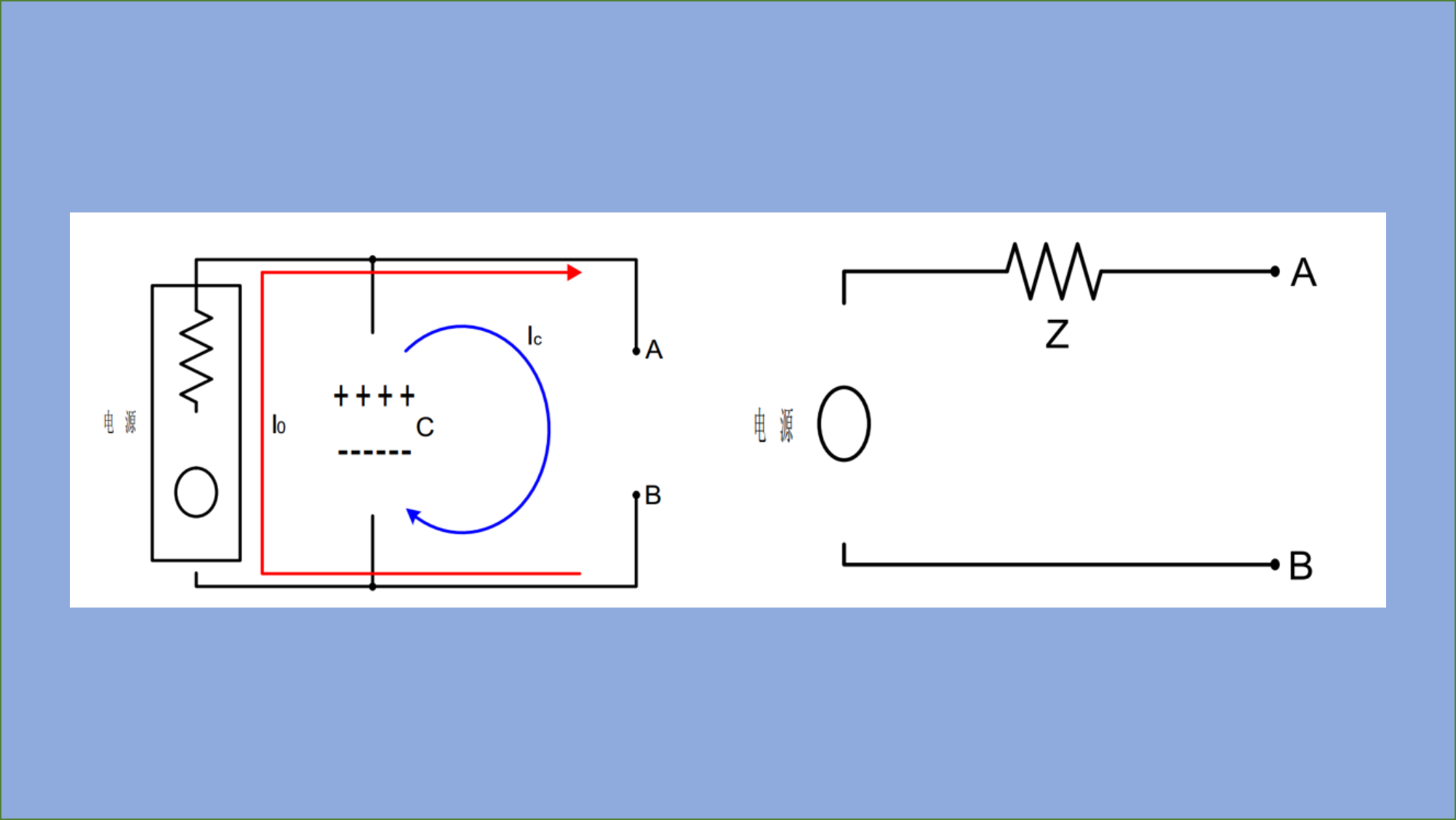

4.1.1 电容的储能作用

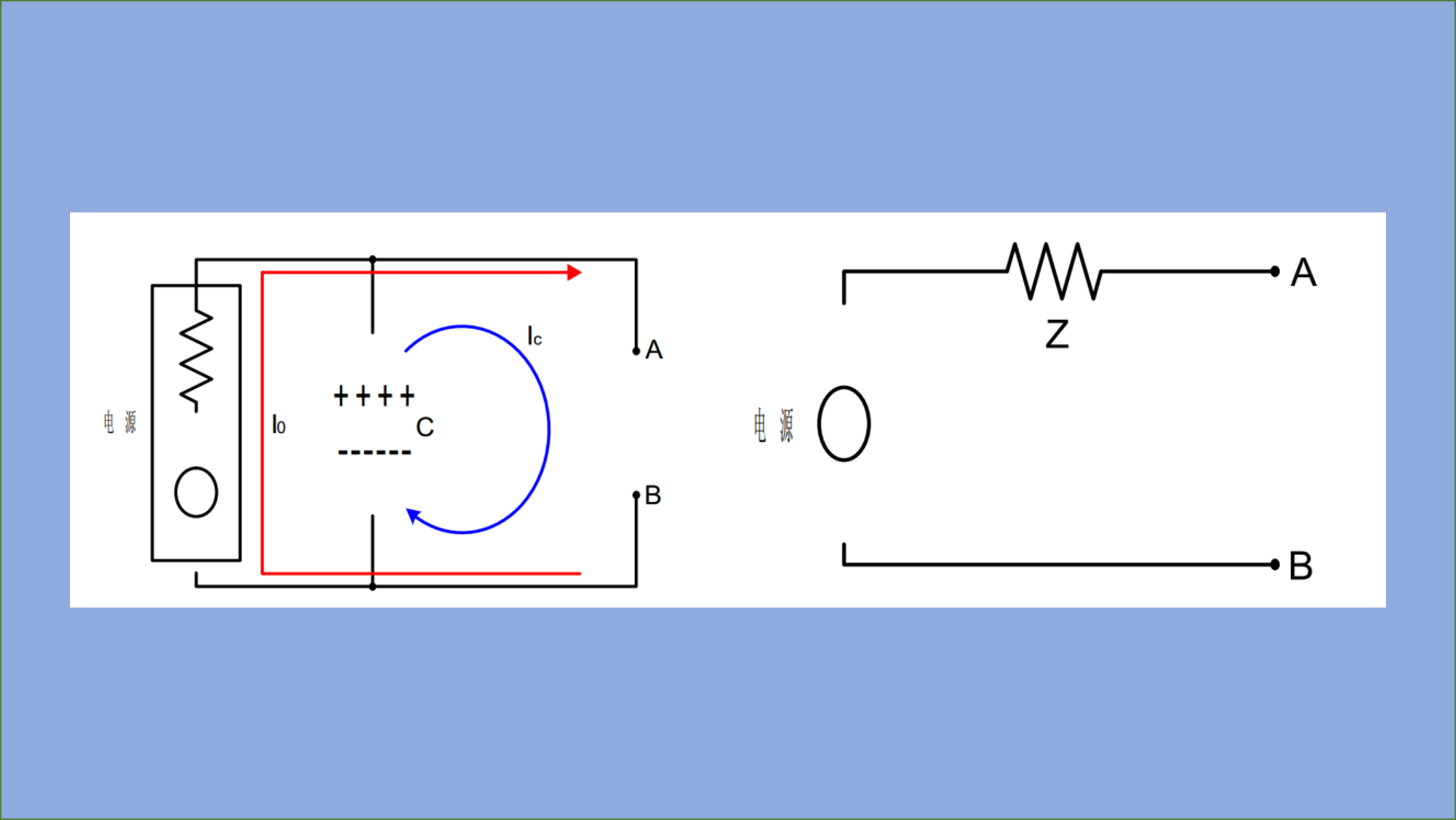

如下图,上电过程中,电源对电容进行充电,一段时间之后电容就存储了一定的电荷量(相当于蓄水池)。如果负载的电流保持不变,即负载上的电压是稳定的,因此电容两端的电压也是恒定的且等于负载两端的电压,此时 Ic = 0,负载的电流由 Io 提供。

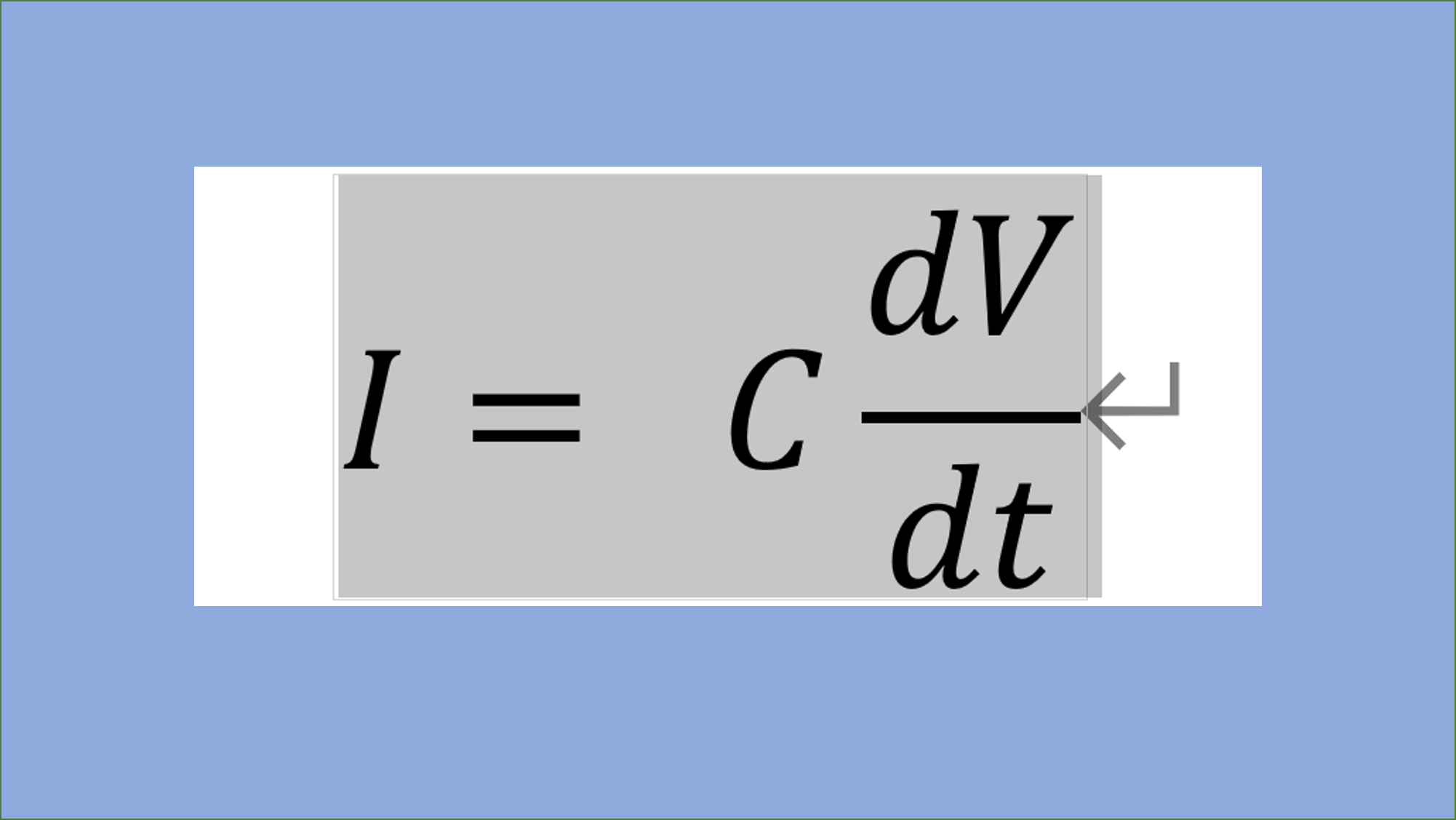

如果负载电流突然发生变化,而晶体管的切换速度极快,稳压源的输出跟不上这种变化,Io 无法及时变化满足负载的变化,就会拉低供电的电压,这时,电容也感知到两端电压的变化,这样电容的变化对应着有电流的产生,Ic 不再为 0,就可以为负载提供一定大小的电流,计算公式如下图。这个过程中,电容分担了稳压源的一部分输出电流。

4.2.1 阻抗

如下图,从右往左看,我们可以把电源和电容复合看做是一个整体的稳压源。

我们要达到的目的是,AB 两点之间的负载电流发生变化,都要尽可能让 AB 两点的电压保持稳定。

对于这个电源模型,我们等效为上述的公式,就可以清晰的知道 I 发生变化,而 V 几乎不变,这就要求阻抗 Z 足够小。电容的特性是:阻直流,通交流。从这个角度来看,耦合电容一定程度上降低了整个电源系统的阻抗。

去耦的关键是做好电容种类和数量的搭配,并非一味的增加总容量。

4.3.3 简化模型

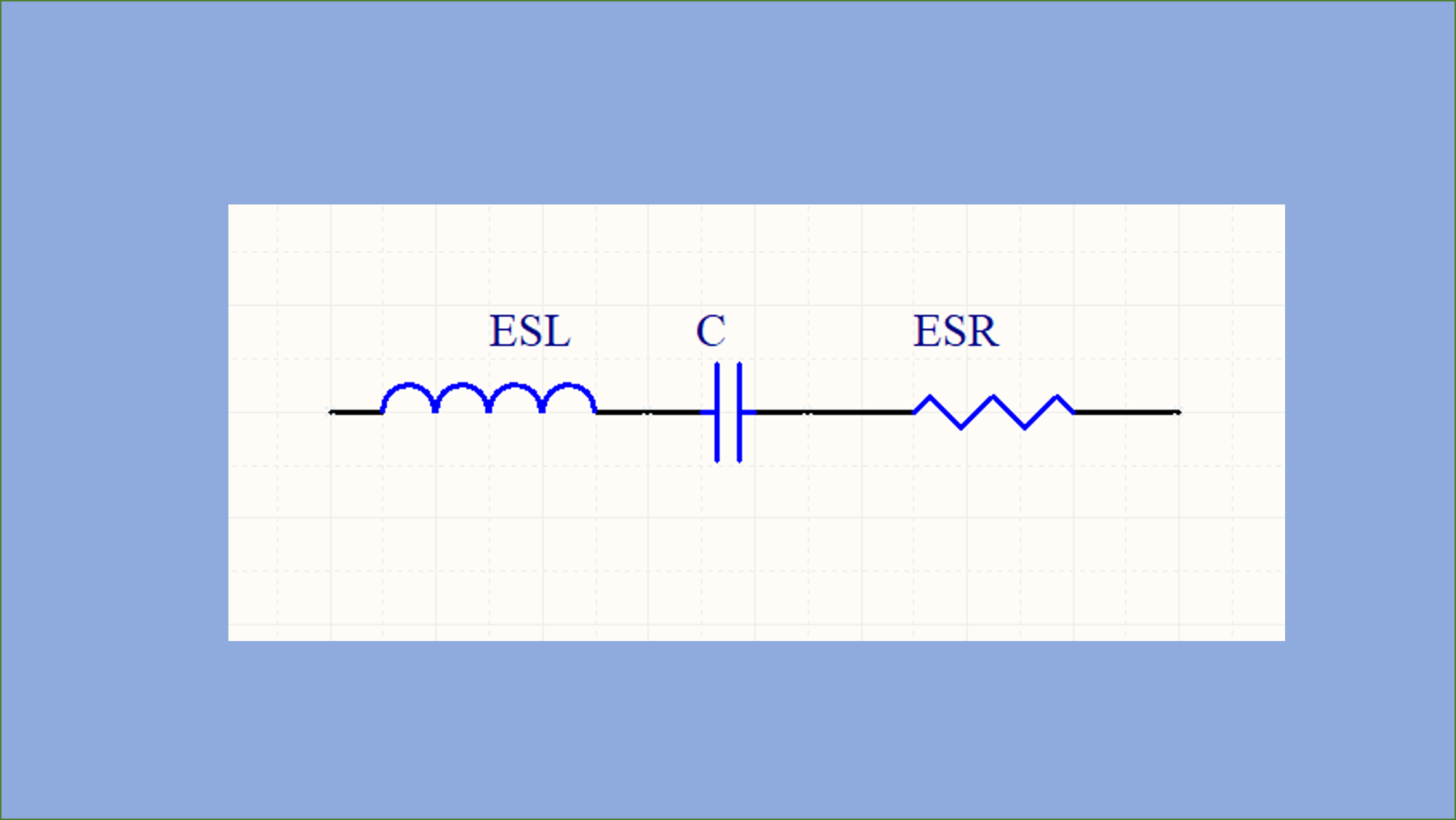

实际的电路之中,电容不仅仅是电容,还有一些等效的参数,如下图所示:

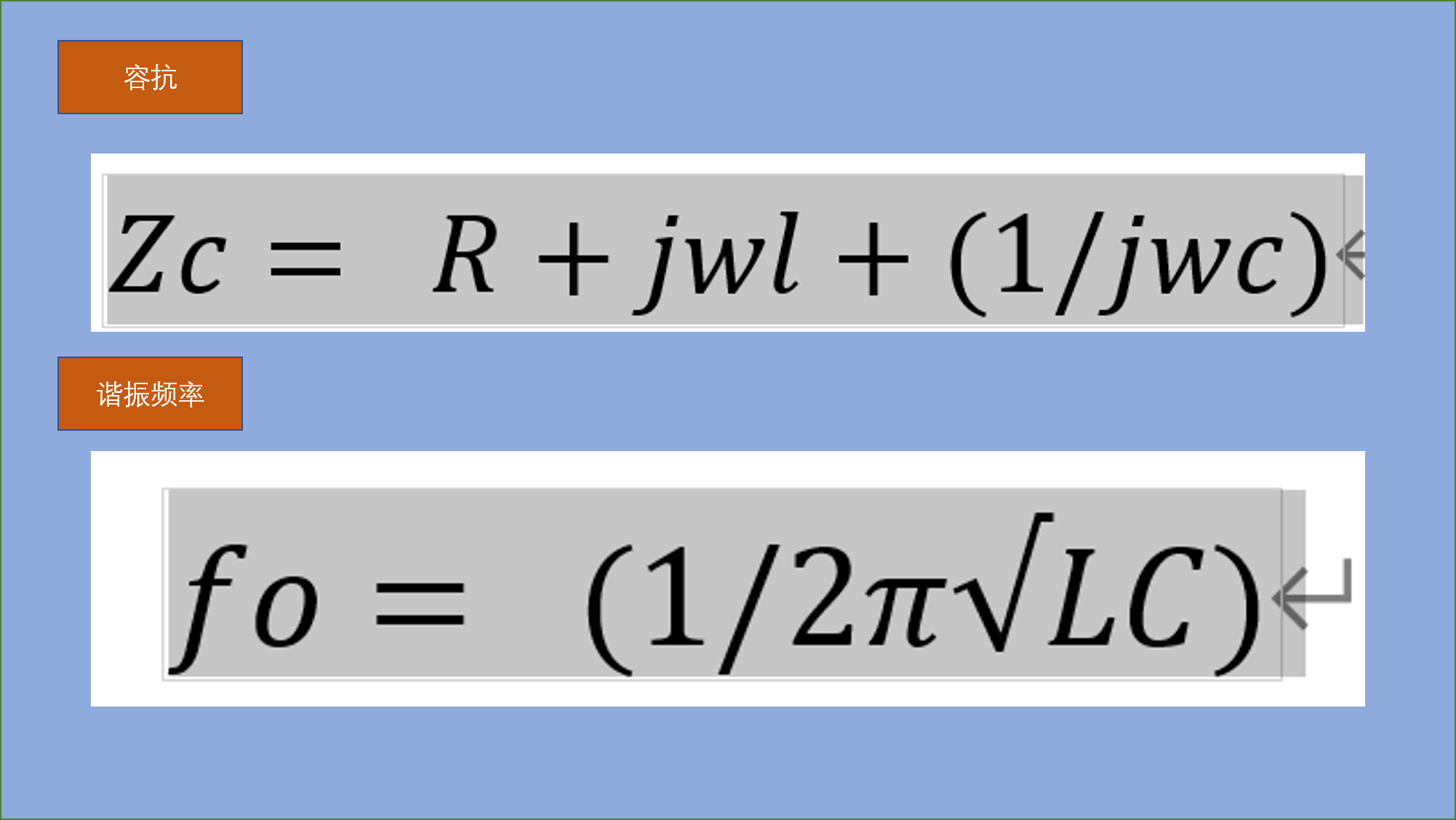

在不同的频段,电容表现出不同的特性。电容的容抗如下;

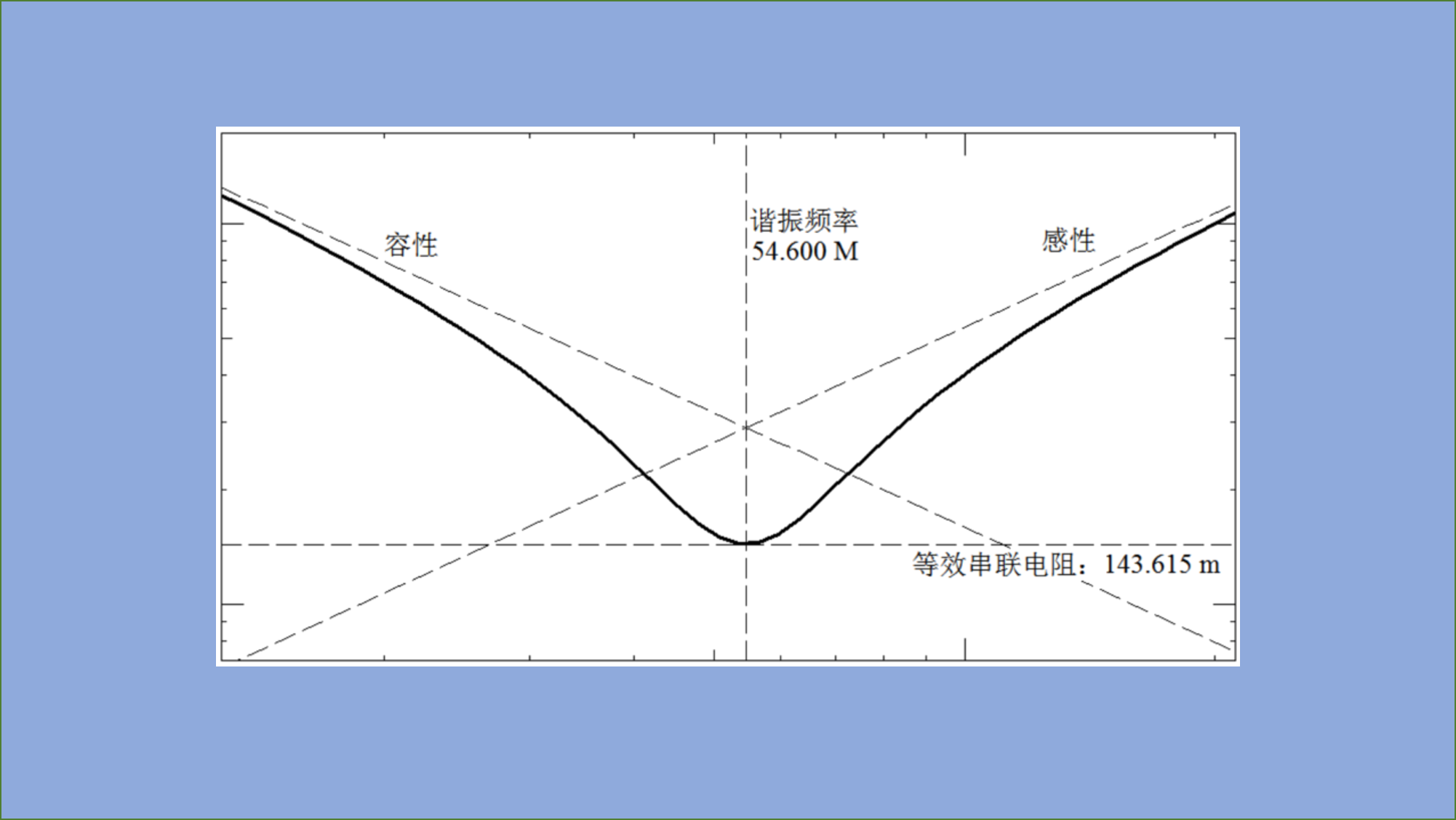

fo 为电容的谐振频率,处在谐振点,电容呈现纯阻特性,小于谐振频率时,呈现容性,大于谐振频率,呈现感性。

然而去耦电容都有一定的工作频率,只有在谐振点的附近,电容才具有最佳的电容特性。

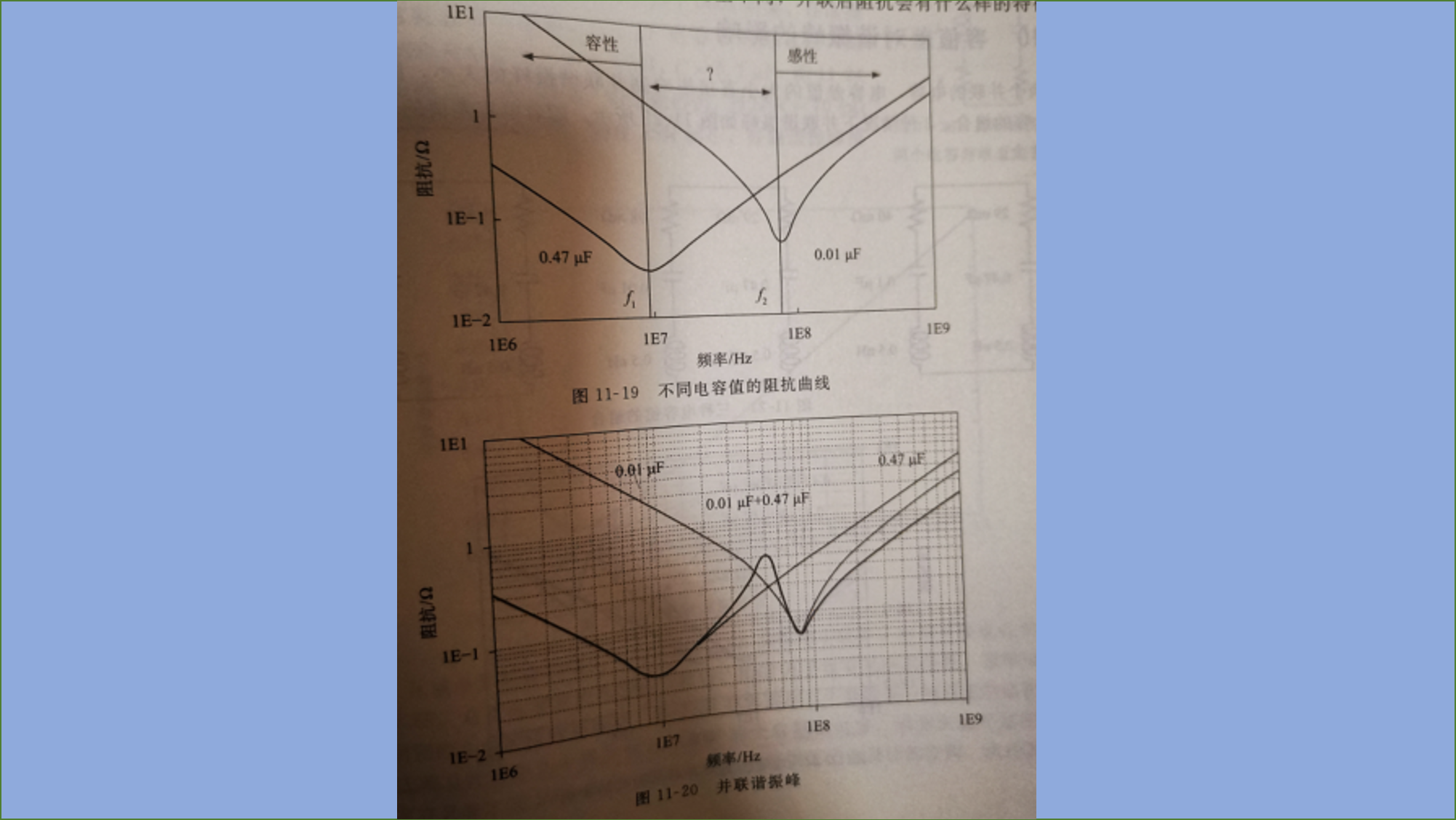

电容的阻抗特性如下图:

不同的电容有不同的谐振频率,如果工作的频率变化范围比较宽,一般采用大电容和小电容并联一起使用。电容越大,谐振点越低。

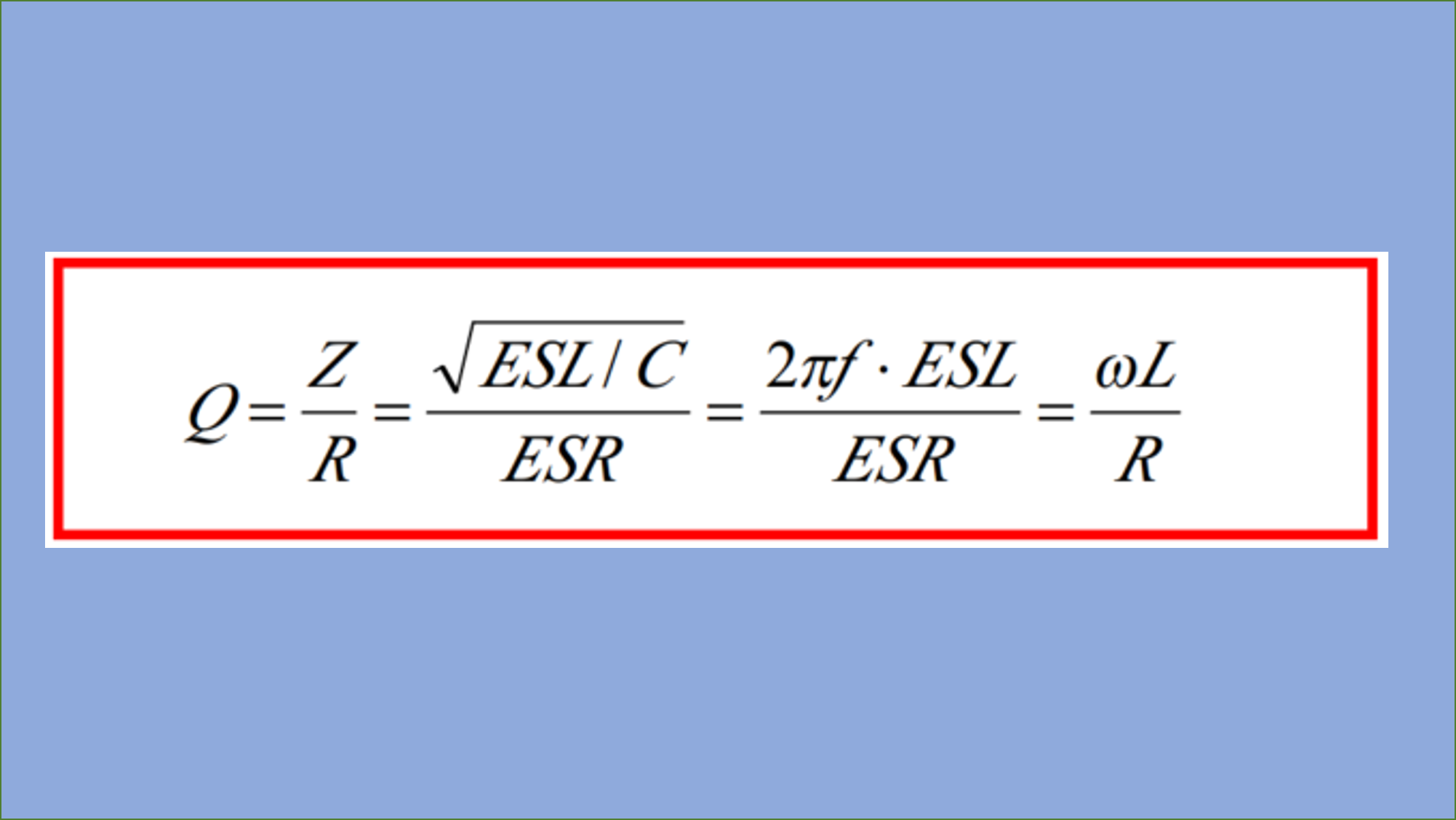

4.3.4 品质因数(Q)

RLC 的串联电路 Q 值定义为:电路串联谐振时,感抗/容抗与纯电阻的比重。Q 值描述的是电路的选频特性,计算公式如下:

Q 值越大,电路的频率选择性越好,允许通过的电流频段越窄。但是在电源去耦的时候,负载芯片上有瞬态电流需求时,去耦电容要立刻给与补偿,如果 Q 值很大,可以流过电容的补偿电流就会变窄,影响电容人的去耦能力,一般用于电源去耦的时候,选择 Q 值较小的电容。一般在板级滤波的时候,会放置一些容量较大的钽电容或电解电容,这两类电容的额 Q 值较低,可以提供比较宽的有效去耦频率范围。

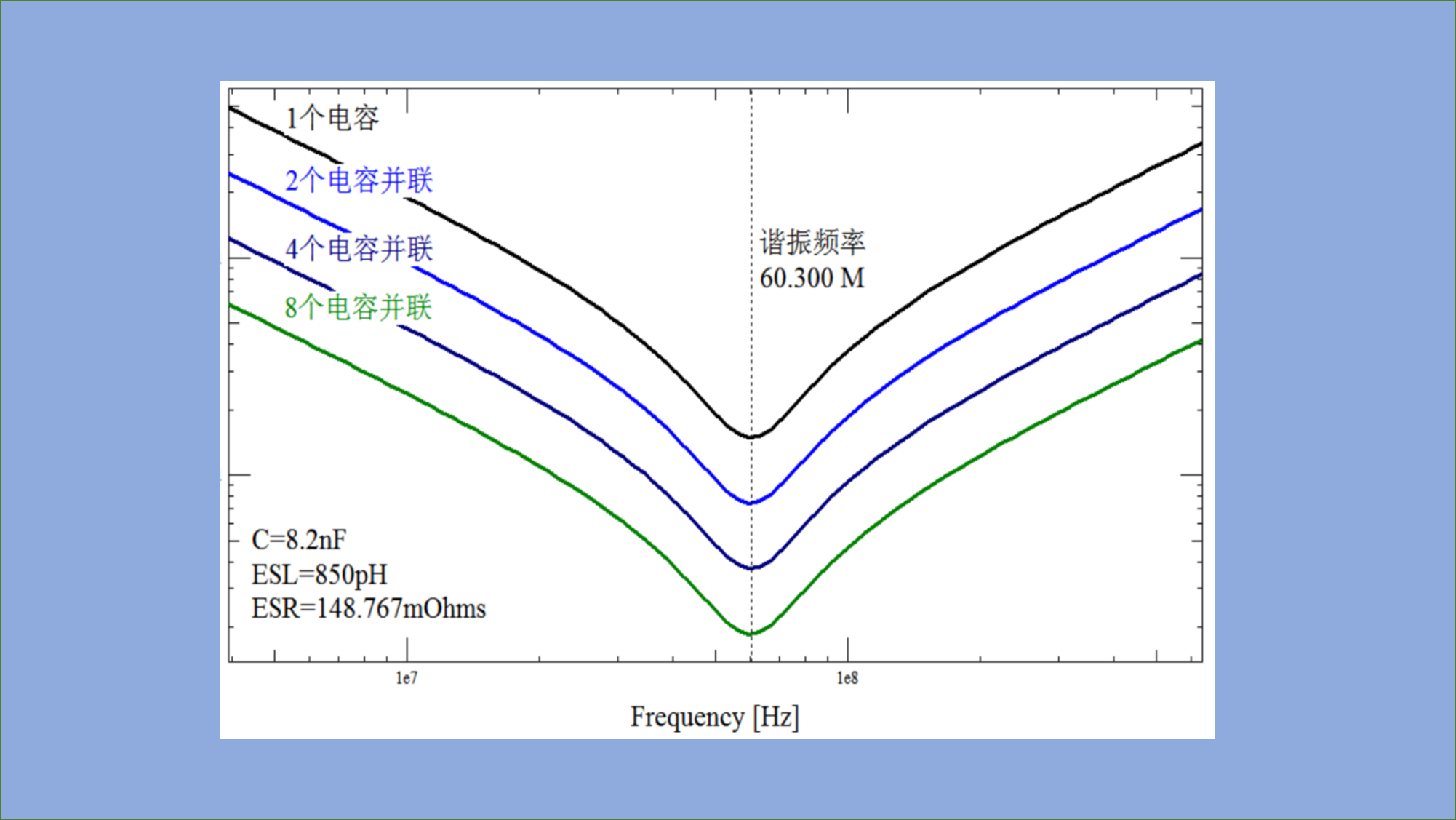

4.3.5 电容并联

(1)相同容值的 n 个电容并联合后,谐振频率不变,阻抗点的阻抗变为了原来的 1/n。

(2)不同容值的电容并联,因为每个电容的谐振频率不一样,当工作频率处于两个谐振频率之间,一些电容表现为容性,一些电容表现为感性,就构成了一个 LC 并联的电路,LC 并联谐振的时候,在两个电容的自谐振频率点之间出现并联谐振峰,如下图所示:

为了使整个 PDN 系统的阻抗小于目标阻抗,必须严格控制并联谐振峰的大小。

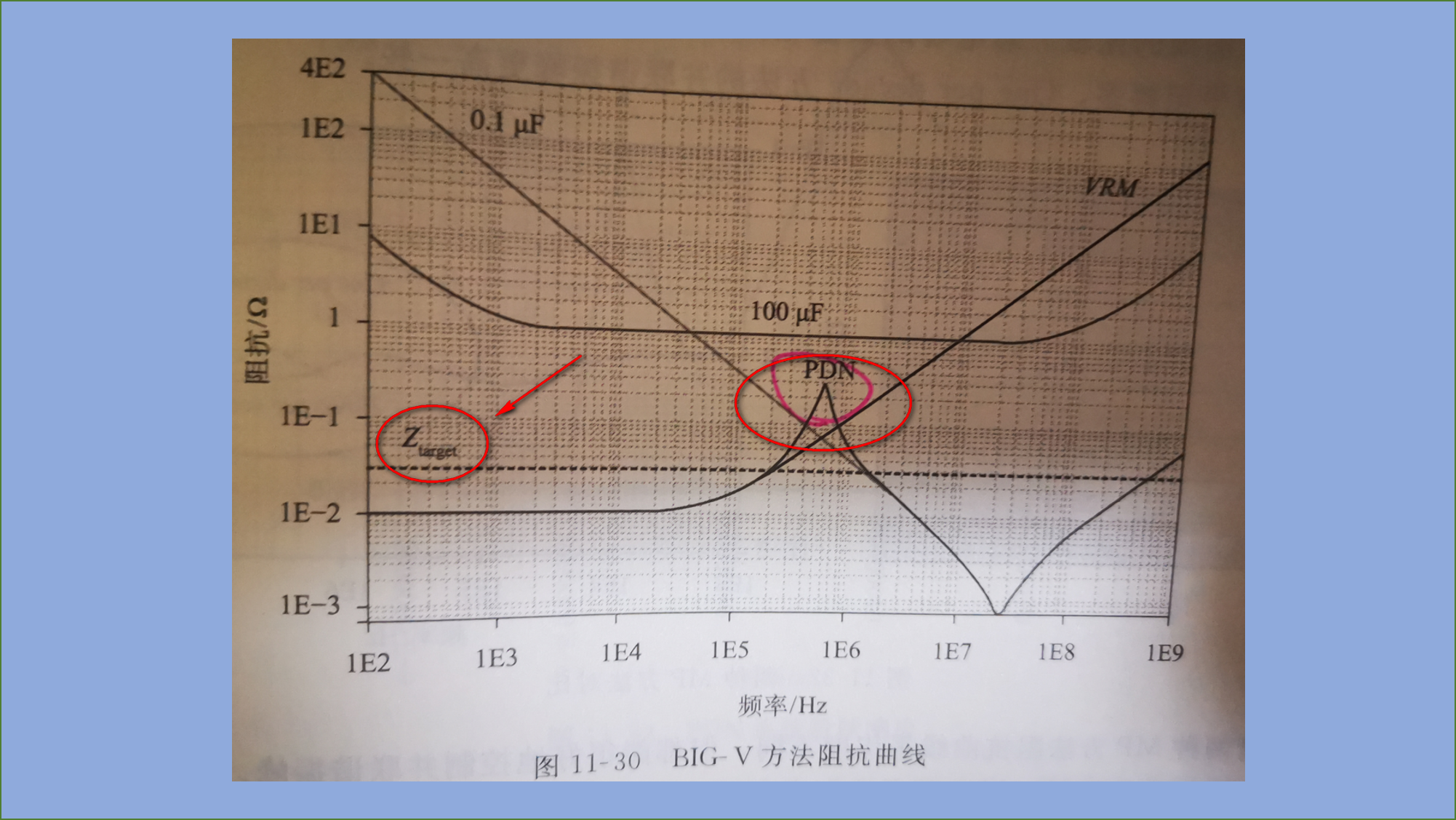

4.3.6 去耦电容的配置方式

(1)Big-V方法:通常的做法就是在芯片每个供电引脚的周围添加几个 0.1uF 的电容,另外再增加几个百微法级别的板级滤波电容。但由前文的介绍可知,同一类型的电容并联使阻抗降低,但跟大电容并联后依然容易形成并联谐振峰,很有可能在 LC 并联形成的并联谐振峰超过了系统的目标阻抗,这个是我们不希望看到的。

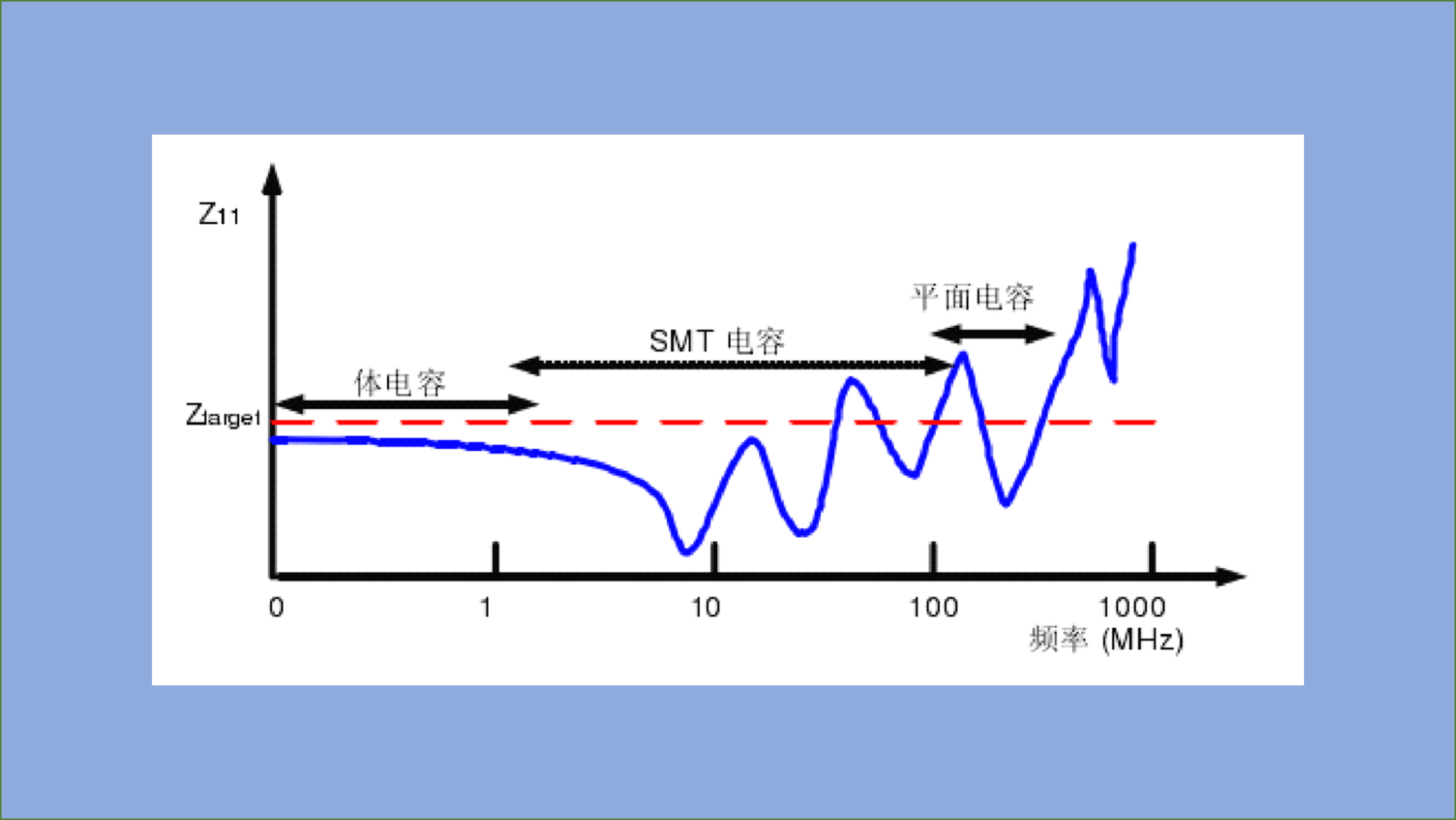

(2)Multi-Pole:使用多种容值的电容并联起来,形成去耦网络。主要分为两种方式:在十倍程的范围内选择一种电容还是三种电容。

| 十倍程一种电容 | 十倍程三种电容 |

|---|---|

| 10uF - 1uF - 0.1uF | 10uF - 4.7uF - 2.2uF - 1uF - 0.47uF - 0.22uF - 0.1uF |

使用 Multi-Pole 方式有比较好的阻抗曲线平坦度,能够满足阻抗一直低于目标阻抗。

各种电容的作用范围如下:

在 PDN 系统中,一般要选择等效串联电阻(ESR)和等效串联电感(ESL)比较低的电容来作为去耦电容。

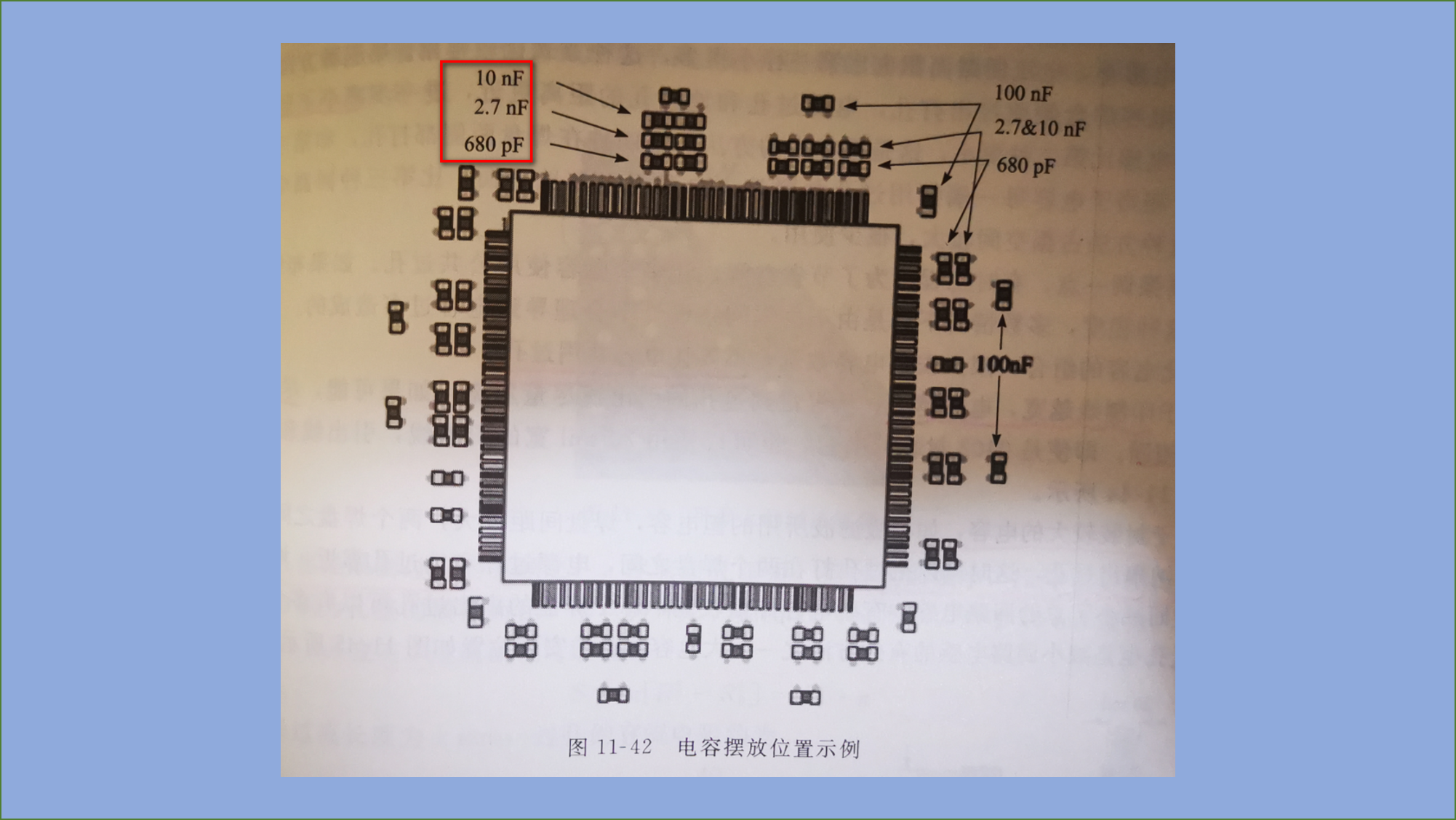

4.3.7 去耦电容的摆放位置

去耦电容的连接方式一段连接芯片的电源引脚,另一端连接地,针对芯片的复杂度和通信速率,分为引脚去耦和平面去耦两种方式。

电容的摆放根据容值的大小放置的位置也有区别,因为不同电容的去耦半径是不一样的,如果摆放的位置已经超出了电容的去耦范围,那么电容的去耦作用也就失效了,所以,根据去耦半径的范围,小电容应该距离芯片的供电引脚近一些,而大电容相对远一些。

,

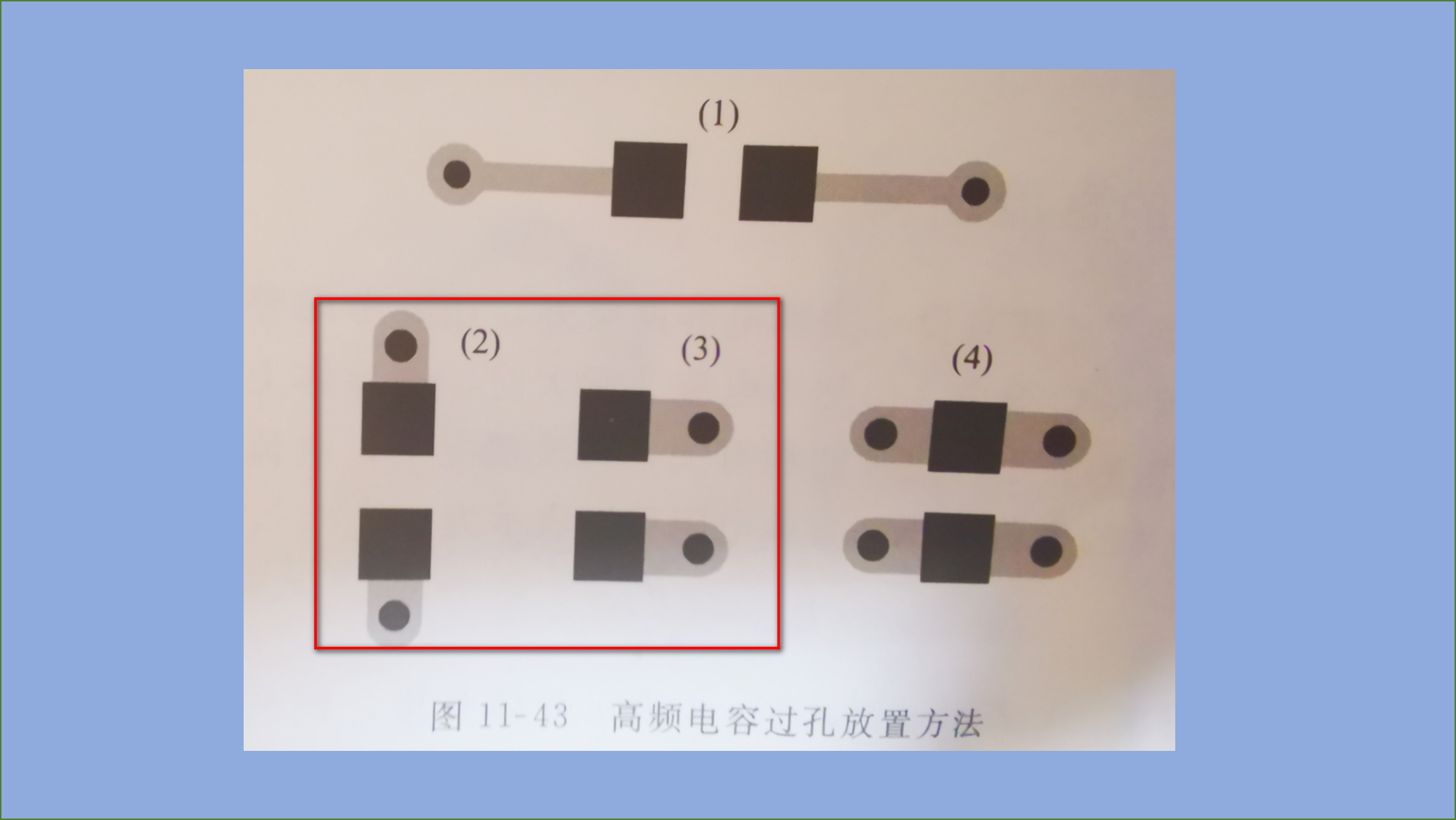

去耦电容的安装核心是减小安装电感。对于在电路板上的连接和过孔的方式是有一定的要求的。原则是:电容引线尽可能的短,电容单独打孔,引线尽可能和焊盘的宽度一致,电源和地之间的回路尽可能小。

上图的(2),(3)是推荐的使用方式,(1)引线又细又长,无疑增加了引线的电感,这与去耦的初衷是相违背的,应该杜绝,(4)是的摆放位置最好,但是占用 PCB 的面积。

4.3.8 目标阻抗设计

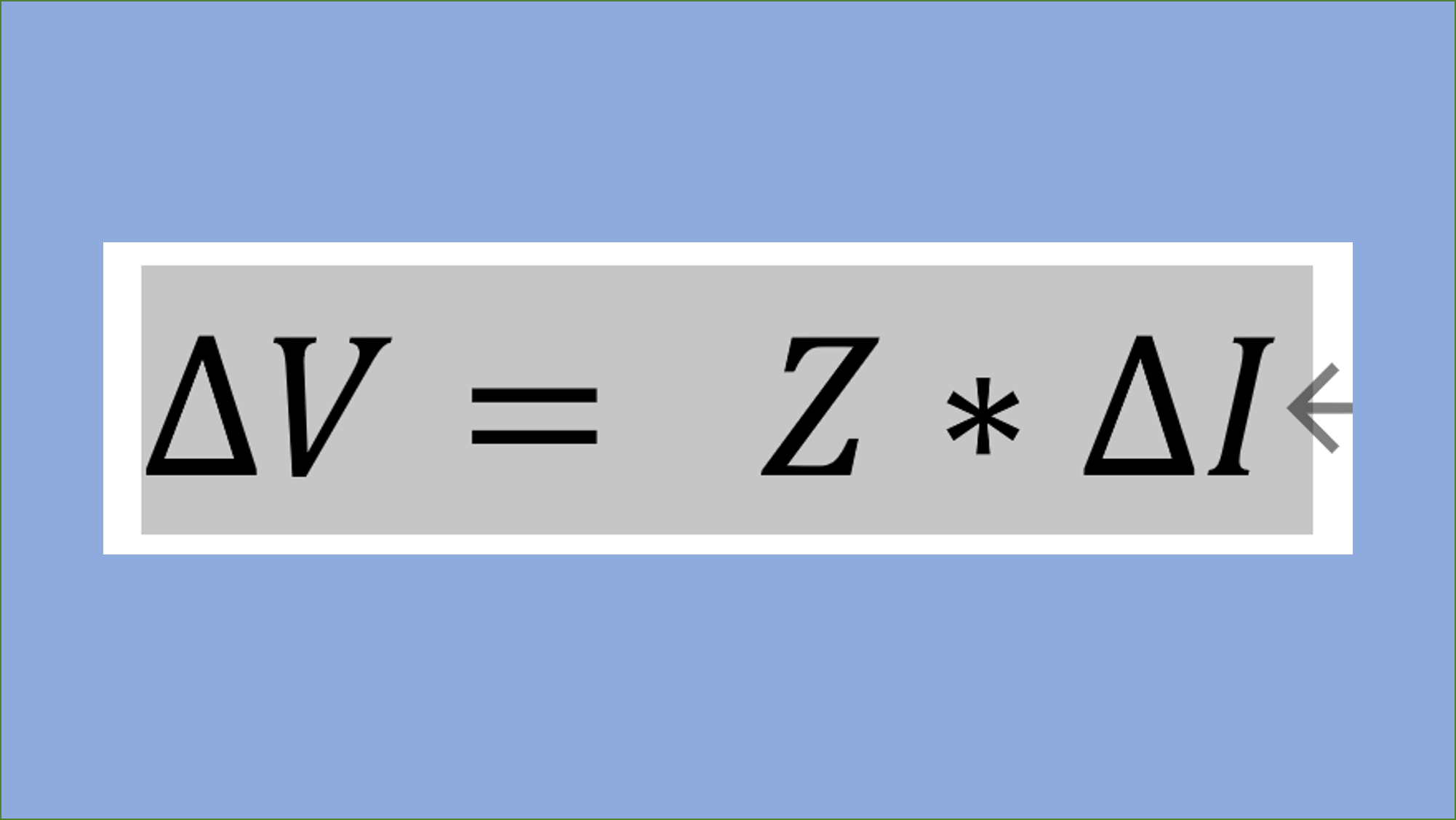

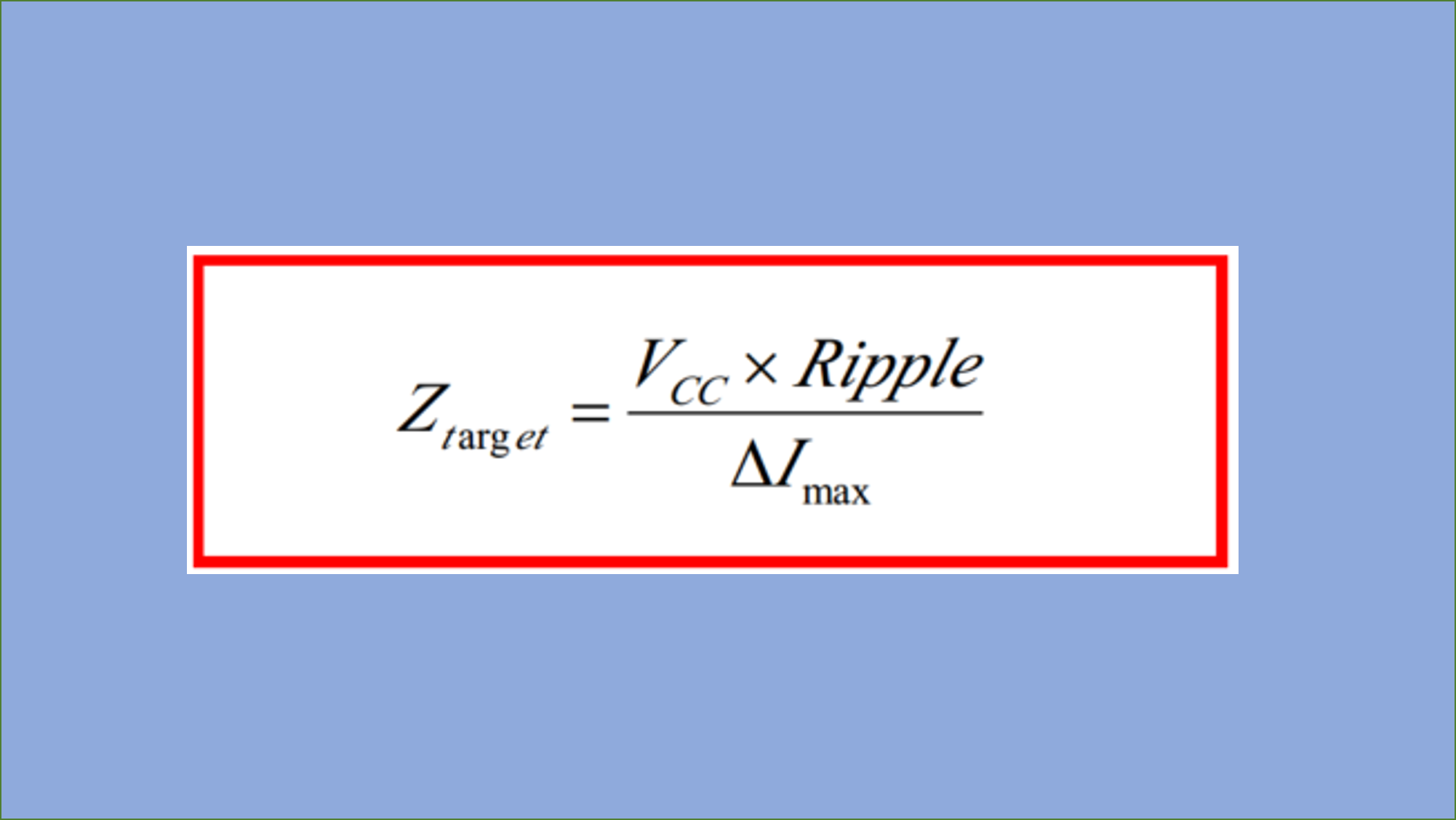

目标阻抗法是目前最具有可操作性的 PDN 系统的去耦方式,核心思想是:利用电流的变化量、阻抗、电压变化量之间的线性约束关系。

PDN 系统的等效模型:

约束关系: ∆V= (Z * ∆I),根据稳压芯片的输出,∆V 我们是可以计算的,只要能够确定负载芯片的最大瞬态电流变化量,那么阻抗 Z 的大小也就对应可以控制,这个最大阻抗就是 PDN 系统的设计目标,系统的阻抗要在工作的频段内低于目标阻抗。目标阻抗的计算方式如下:

参数介绍:

| 参数 | 解释 |

|---|---|

| Ztarget | 目标阻抗 |

| Vcc | 芯片的供电,比如常见的:5V/3.3V/1.8V等 |

| Ripple | 允许的电压波动,比如±5%,±3 等 |

| ∆Imax | 负载芯片的最大瞬态电流 |

为了保证信号的完整性,电源分配系统的阻抗必须低于目标阻抗。

5. 总结一下

本文主要是个人在学习电源完整性过程中的一些笔记总结,用于经常复习,参考的连接在文末已给出,感谢他们。本人能力有限,表述记录的过程中难免有疏漏,欢迎大家积极交流讨论。

解决直流压降的核心是:尽可能增大供电电路上的过流面积,采取的措施有加宽电源层,地平面的宽度,我们可以见到一般高速复杂的 PCB 都需要提供单独的电源层和地层;另外就是减少电源的回路面积,缩短电源到芯片的距离,增加铜箔厚度等措施。

欢迎关注公众号:【千艺千寻】,共同成长